MOSFET은 반도체 산업의 가장 기본적인 부품 중 하나입니다. 전자회로에서는 MOSFET이 일반적으로 전력증폭회로나 스위칭 전원회로에 사용되며 널리 사용되고 있다. 아래에,올키MOSFET의 작동 원리에 대해 자세히 설명하고 MOSFET의 내부 구조를 분석합니다.

무엇인가요MOSFET

MOSFET, 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET). 아날로그 회로와 디지털 회로에 널리 사용될 수 있는 전계효과 트랜지스터이다. "채널"(작동 캐리어)의 극성 차이에 따라 NMOS 및 PMOS라고도 불리는 "N형"과 "P형"의 두 가지 유형으로 나눌 수 있습니다.

MOSFET 작동 원리

MOSFET은 동작 모드에 따라 향상형(enhanced type)과 공핍형(depletion type)으로 나눌 수 있습니다. 향상 유형은 바이어스 전압이 적용되지 않고 아무런 문제가 없는 MOSFET을 나타냅니다.유도 채널. 공핍형은 바이어스 전압이 인가되지 않은 경우의 MOSFET을 나타냅니다. 전도성 채널이 나타납니다.

실제 애플리케이션에는 N채널 강화형 MOSFET과 P채널 강화형 MOSFET만 있습니다. NMOSFET은 온 상태 저항이 작고 제조가 용이하기 때문에 실제 응용 분야에서는 PMOS보다 NMOS가 더 일반적입니다.

강화 모드 MOSFET

강화 모드 MOSFET의 드레인 D와 소스 S 사이에는 2개의 백투백 PN 접합이 있습니다. 게이트-소스 전압 VGS=0인 경우, 드레인-소스 전압 VDS를 더해도 항상 PN 접합이 역바이어스 상태로 존재하며, 드레인과 소스 사이에 전도성 채널이 없습니다(전류가 흐르지 않음). ). 따라서 이때 드레인 전류 ID는 0이다.

이때 게이트와 소스 사이에 순방향 전압이 추가되면. 즉, VGS>0이면 게이트가 P형 실리콘 기판과 정렬된 전기장이 게이트 전극과 실리콘 기판 사이의 SiO2 절연층에 생성됩니다. 산화물 층은 절연성이므로 게이트에 인가되는 전압 VGS는 전류를 생성할 수 없습니다. 산화물층 양면에 커패시터가 생성되고, VGS 등가회로는 이 커패시터(커패시터)를 충전한다. 그리고 게이트의 양의 전압에 이끌려 VGS가 천천히 상승하면서 전기장을 생성합니다. 많은 수의 전자가 이 커패시터(커패시터)의 반대편에 축적되어 드레인에서 소스까지 N형 전도성 채널을 생성합니다. VGS가 튜브의 턴온 전압 VT(일반적으로 약 2V)를 초과하면 N 채널 튜브가 전도되기 시작하여 드레인 전류 ID가 생성됩니다. 채널이 처음으로 턴온 전압을 생성하기 시작할 때 게이트-소스 전압을 호출합니다. 일반적으로 VT로 표현됩니다.

게이트 전압(VGS)의 크기를 조절하면 전계의 강약이 달라지며, 드레인 전류(ID)의 크기를 조절하는 효과를 얻을 수 있다. 이는 전기장을 이용해 전류를 제어하는 MOSFET의 중요한 특징이기도 해서 전계효과 트랜지스터라고도 불린다.

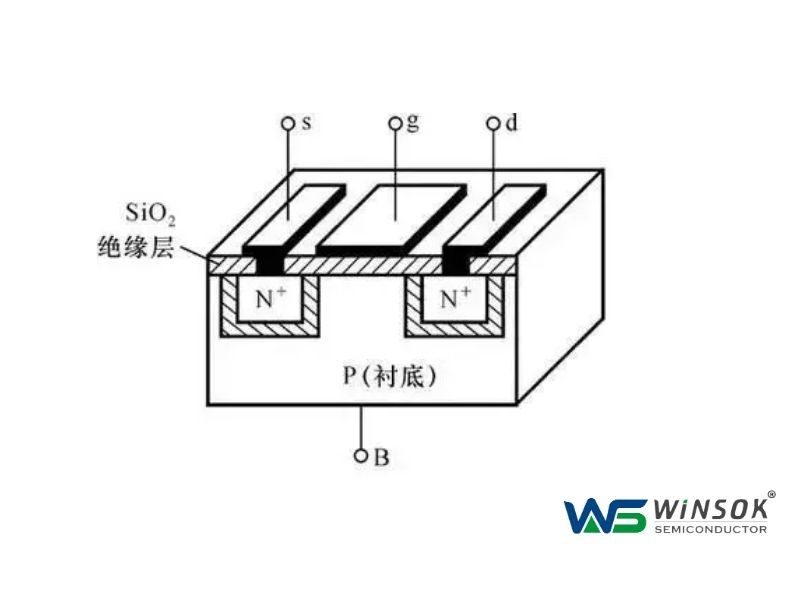

MOSFET 내부 구조

불순물 농도가 낮은 P형 실리콘 기판 위에 불순물 농도가 높은 N+ 영역을 두 개 만들고, 두 개의 전극을 금속 알루미늄으로 인출해 각각 드레인(d)과 소스(s) 역할을 한다. 그런 다음 반도체 표면을 매우 얇은 이산화규소(SiO2) 절연층으로 덮고, 드레인과 소스 사이의 절연층 위에 알루미늄 전극을 설치하여 게이트(g) 역할을 한다. 전극 B도 기판 위에 인출되어 N채널 강화 모드 MOSFET을 형성합니다. P채널 강화형 MOSFET의 내부 형성에 대해서도 마찬가지이다.

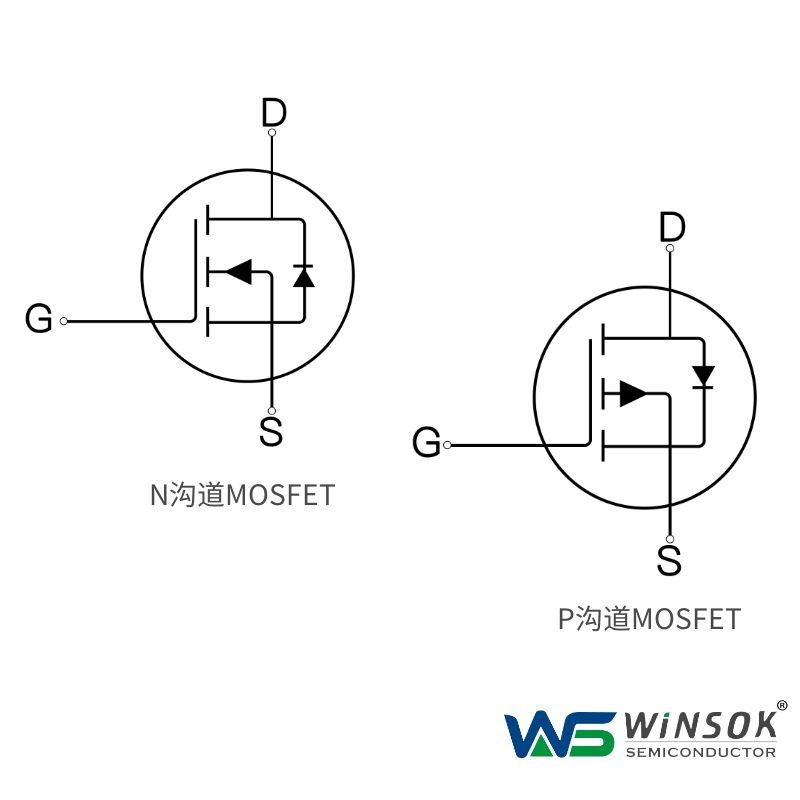

N채널 MOSFET 및 P채널 MOSFET 회로 기호

위 그림은 MOSFET의 회로 기호를 보여줍니다. 그림에서 D는 드레인, S는 소스, G는 게이트, 가운데 화살표는 기판을 나타냅니다. 화살표가 안쪽을 가리키면 N채널 MOSFET을 나타내고, 화살표가 바깥쪽을 가리키면 P채널 MOSFET을 나타냅니다.

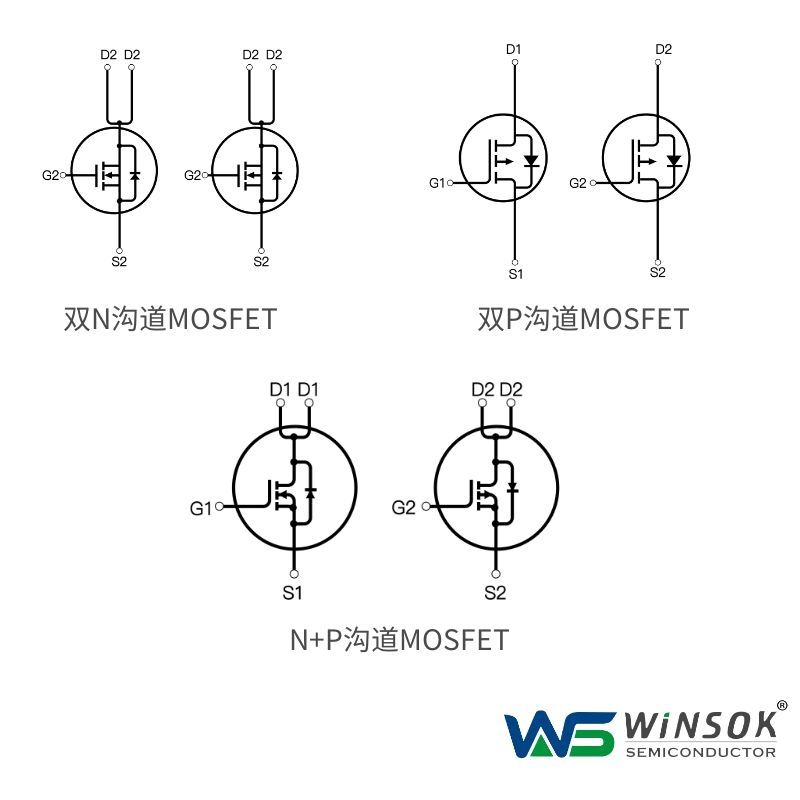

듀얼 N채널 MOSFET, 듀얼 P채널 MOSFET 및 N+P채널 MOSFET 회로 기호

실제로 MOSFET 제조 과정에서 기판은 공장에서 출고되기 전에 소스에 연결됩니다. 따라서 기호 규칙에서는 기판을 나타내는 화살표 기호도 소스와 연결하여 드레인과 소스를 구분해야 합니다. MOSFET에 사용되는 전압의 극성은 기존 트랜지스터와 유사합니다. N채널은 NPN 트랜지스터와 유사합니다. 드레인 D는 양극에 연결되고, 소스 S는 음극에 연결된다. 게이트 G가 양의 전압을 가지면 전도성 채널이 형성되고 N채널 MOSFET이 작동하기 시작합니다. 마찬가지로 P 채널은 PNP 트랜지스터와 유사합니다. 드레인 D는 음극에 연결되고, 소스 S는 양극에 연결되며, 게이트 G가 음의 전압을 가지면 전도성 채널이 형성되고 P채널 MOSFET이 작동하기 시작한다.

MOSFET 스위칭 손실 원리

NMOS이든 PMOS이든 전원을 켠 후에 전도 내부 저항이 생성되므로 전류는 이 내부 저항에서 에너지를 소비하게 됩니다. 소비되는 에너지의 이 부분을 전도 소비라고 합니다. 전도 내부 저항이 작은 MOSFET을 선택하면 전도 소비를 효과적으로 줄일 수 있습니다. 현재 저전력 MOSFET의 내부 저항은 일반적으로 수십 밀리옴 정도이며, 수 밀리옴도 있습니다.

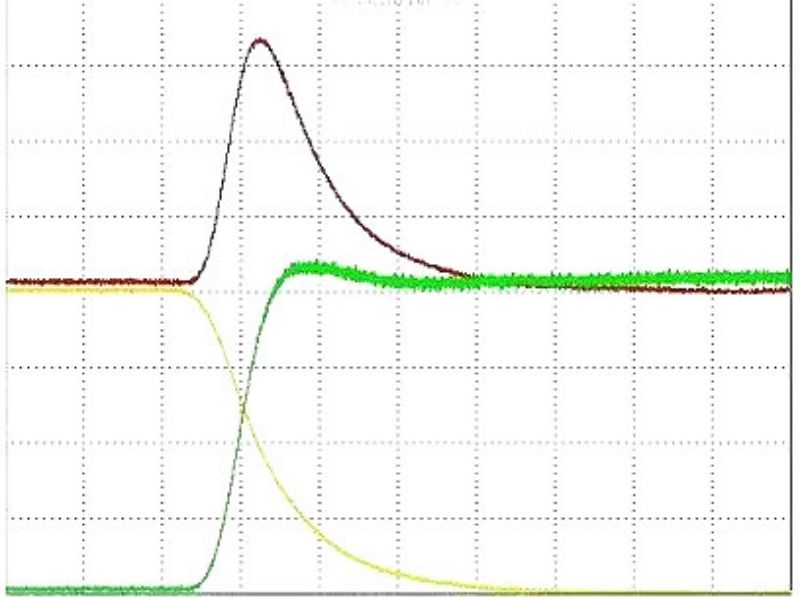

MOS가 켜지고 종료되면 순간적으로 구현되어서는 안됩니다. MOS 양쪽의 전압은 효과적으로 감소하고 이를 통해 흐르는 전류는 증가합니다. 이 기간 동안 MOSFET의 손실은 전압과 전류의 곱, 즉 스위칭 손실입니다. 일반적으로 스위칭 손실은 전도 손실보다 훨씬 크며, 스위칭 주파수가 빠를수록 손실도 커집니다.

도통 순간의 전압과 전류의 곱은 매우 커서 손실도 매우 크다. 스위칭 손실은 두 가지 방법으로 줄일 수 있습니다. 하나는 스위칭 시간을 줄여 각 턴온 시 손실을 효과적으로 줄일 수 있다는 것입니다. 다른 하나는 스위칭 주파수를 줄여 단위 시간당 스위치 수를 줄이는 것입니다.

위의 내용은 MOSFET의 동작원리도와 MOSFET의 내부구조 분석에 대한 자세한 설명이다. MOSFET에 대해 자세히 알아보려면 OLUKEY에 문의하여 MOSFET 기술 지원을 받으세요!