D-FET는 채널이 존재할 때 0 게이트 바이어스에 있고 FET를 전도할 수 있습니다. E-FET는 채널이 없을 때 0 게이트 바이어스에 있으며 FET를 전도할 수 없습니다. 이 두 가지 유형의 FET는 고유한 특성과 용도를 가지고 있습니다. 일반적으로 고속, 저전력 회로의 향상된 FET는 매우 중요합니다. 이 장치가 작동 중이면 게이트 바이어스 vo의 극성입니다.ltage 및 배수 동일한 전압이면 회로 설계에 더 편리합니다.

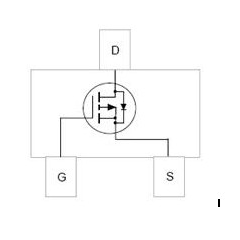

소위 강화란 VGS = 0 튜브가 차단 상태에 올바른 VGS를 더한 경우 대부분의 캐리어가 게이트로 끌어당겨 해당 영역의 캐리어를 "강화"하여 전도성 채널을 형성한다는 의미입니다. n채널 강화 MOSFET은 기본적으로 좌우 대칭 토폴로지이며, 이는 SiO2 필름 절연층 생성 시 P형 반도체입니다. P형 반도체 위에 SiO2막의 절연층을 생성한 후, 두 개의 고농도로 도핑된 N형 영역을 확산시킵니다.포토리소그래피, N형 영역의 전극을 리드합니다. 하나는 드레인 D용이고 다른 하나는 소스 S용입니다. 알루미늄 금속 층은 게이트 G로서 소스와 드레인 사이의 절연층에 도금됩니다. VGS = 0V일 때 , 드레인과 소스 사이에 다이오드가 백투백으로 연결된 다이오드가 꽤 많이 있으며 D와 S 사이의 전압은 D와 S 사이에 전류를 형성하지 않습니다. D와 S 사이의 전류는 인가되는 전압에 의해 형성되지 않습니다 .

게이트 전압을 가할 때 0 < VGS < VGS(th)이면 게이트와 기판 사이에 형성된 용량성 전계를 통해 게이트 하단 부근의 P형 반도체에 있는 폴리온 홀이 아래쪽으로 밀어내게 되고, 음이온의 얇은 공핍층이 나타납니다. 동시에 그 안의 올리고곤을 끌어당겨 표면층으로 이동하게 되지만 그 수가 제한되어 있고 드레인과 소스를 연결하는 전도성 채널을 형성하기에는 부족하여 여전히 드레인 전류(ID)를 형성하기에는 부족하다. 추가 증가 VGS, VGS일 때 > VGS(th)(VGS(th)를 턴온 전압이라고 함), 이때 게이트 전압이 상대적으로 강했기 때문에 게이트 하단 근처의 P형 반도체 표면층 아래에 더 많은 전류가 모여 있습니다. 전자를 사용하면 트렌치, 배수구 및 통신 소스를 형성할 수 있습니다. 이때 드레인 소스 전압을 가하면 드레인 전류가 형성될 수 있다. P형 반도체의 캐리어 홀과 극성이 반대이기 때문에 게이트 아래에 형성된 전도성 채널의 전자를 안티형 층이라고 합니다. VGS가 계속 증가함에 따라 ID도 계속 증가할 것입니다. VGS = 0V에서 ID = 0이고, 드레인 전류는 VGS > VGS(th) 이후에만 발생하므로 이러한 유형의 MOSFET을 향상 MOSFET이라고 합니다.

드레인 전류에 대한 VGS의 제어 관계는 전달 특성 곡선이라고 불리는 iD = f(VGS(th))|VDS=const 곡선과 전달 특성 곡선의 기울기 크기 gm으로 설명할 수 있습니다. 게이트 소스 전압에 의한 드레인 전류 제어를 반영합니다. gm의 크기는 mA/V이므로 gm은 상호컨덕턴스라고도 합니다.